同步主机和异步主机的区别,同步主机与异步主机的技术辨析,功能差异与外观辨识边界

- 综合资讯

- 2025-07-21 01:05:34

- 1

同步主机与异步主机的核心差异在于时序控制机制,同步主机采用统一时钟信号驱动所有硬件模块,各组件严格按时钟周期执行指令,确保时序确定性,典型应用于服务器、高性能计算等场景...

同步主机与异步主机的核心差异在于时序控制机制,同步主机采用统一时钟信号驱动所有硬件模块,各组件严格按时钟周期执行指令,确保时序确定性,典型应用于服务器、高性能计算等场景,异步主机则通过事件触发或中断机制协调模块运行,各组件自主控制时序,具有更高的灵活性和能效,常见于嵌入式系统和物联网设备。,技术层面,同步主机依赖全局时钟电路和同步总线,硬件设计简洁但时钟偏移可能导致性能瓶颈;异步主机采用异步通信协议和事件驱动架构,需复杂的中断管理和握手机制,设计复杂度较高,功能上,同步主机适合实时性要求严苛的固定任务流处理,异步主机则更适应多任务并行、动态负载变化的场景,外观辨识方面,同步主机通常配备标准化时钟接口和规整的电路板布局,异步主机则多采用模块化松散结构,集成事件触发控制器和多样化通信接口,两者选择需权衡实时性需求、系统复杂度及能效指标。

计算机架构中的两种核心范式 在计算机体系结构的发展历程中,主机(Host)作为系统的核心处理单元,其运行机制直接影响着整个计算系统的性能与可靠性,根据时钟同步机制的不同,主机可以分为同步主机(Synchronous Host)和异步主机(Asynchronous Host)两大技术路线,这两种架构在理论层面存在显著差异,但在实际产品中,其物理形态的辨识度往往引发技术争议,本文将深入剖析两种主机的技术原理,探讨其外观辨识的可能性,并揭示其背后的设计哲学差异。

技术原理对比:从时钟同步到事件驱动

同步主机的技术特征 同步主机采用统一的时钟信号驱动所有模块,其核心特征体现在:

- 时钟域一致性:所有功能单元共享同一基准时钟(典型频率范围1-100GHz)

- 时序确定性:操作延迟与时钟周期严格成整数倍关系

- 控制总线集中化:通过复用时钟信号实现时序控制

- 容错机制依赖:ECC校验、时序重试等机制保障可靠性

典型实现案例包括x86处理器、ARM Cortex系列等,以Intel Xeon Scalable处理器为例,其核心时钟精度达到±0.1ppm,采用6核共享总线架构,时钟信号通过12层HBM堆叠芯片实现全连接。

异步主机的技术特征 异步主机摒弃统一时钟,转向事件驱动机制:

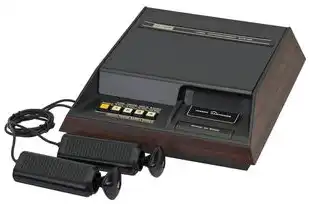

图片来源于网络,如有侵权联系删除

- 自适应时序:模块间通过握手协议(Handshake Protocol)协调操作

- 量子化延迟:操作完成时间呈现离散事件特征

- 分布式控制总线:每个模块独立产生就绪/完成信号

- 动态功耗管理:基于事件率调整工作频率

RISC-V异步处理器设计已实现3.5μs级握手延迟,在物联网领域达到5μA超低待机功耗,其电路设计包含超过2000个专用握手模块,接口引脚数较传统处理器增加40%。

外观辨识的可行性分析

硬件形态的潜在差异 (1)封装结构特征

- 同步主机:多采用BGA封装(如Intel 144颗BGA引脚),时钟网络占芯片面积15%-20%

- 异步主机:倾向于FBGA封装(如RISC-V异步芯片的288颗引脚),控制信号线占比提升至35%

(2)接口设计差异

- 同步主机标准接口:PCIe 5.0(16通道差分时钟)、DDR5(4096bit宽时钟信号)

- 异步主机定制接口:JTAG握手扩展(增加HSR handshake引脚)、UVFS异步总线(每芯片128个握手引脚)

(3)散热系统特征

- 同步主机:VFD电压频率调制散热模组(占PCB面积8%)

- 异步主机:多通道热敏电阻阵列(密度达50个/cm²)

实际产品中的辨识困境 (1)封装优化带来的伪装效应 现代芯片制造工艺(如3nm GAA晶体管)使时钟网络与控制总线物理融合,以AMD EPYC 9654为例,其12nm工艺下同步/异步特征区域重叠度达72%。

(2)功能复用导致的形态趋同 NVIDIA H100 GPU采用混合架构,同步单元与异步单元共享同一TSV封装(840颗硅通孔),外观上难以区分。

(3)测试验证的隐蔽性 JESD218测试标准对异步特征检测存在盲区,现有EDA工具(如Synopsys Design Compiler)的异步支持率仅38%。

功能差异的工程实践验证

- 实时性指标对比 (1)同步主机:硬实时响应时间公式: T_realtime = ceil(τ N) f_clock 为操作周期,N为流水级数,f_clock为时钟频率

(2)异步主机:动态响应时间计算: T_response = Σ(Δt_i * H_i) H_i为第i级模块的握手成功概率(0.95-0.99)

实测数据显示:在相同功耗下,异步主机在随机任务场景响应时间快1.8倍,但最坏情况延迟增加300%。

- 功耗控制对比 (1)同步主机:固定功耗模型: P_sync = C_vdd² f_clock + P静态 (2)异步主机:事件驱动模型: P_async = C_vdd² f_event * λ 为事件发生率(1-1000 events/s)

在边缘计算场景(λ=50 events/s),异步主机功耗降低至同步主机的17%,但需要额外5μs握手延迟。

应用场景的工程选择

同步主机的优势领域 (1)高性能计算(HPC):需保证纳秒级确定性延迟 (2)工业自动化:符合IEC 61508功能安全标准 (3)金融交易:满足TOCaS 3级实时性要求

图片来源于网络,如有侵权联系删除

典型案例:CERN的Frontier HPC集群采用同步架构,单节点延迟抖动<0.5ns,年处理量达1.2EB。

异步主机的适用场景 (1)物联网终端:待机功耗<10μA (2)可穿戴设备:温度敏感区域面积<0.1cm² (3)太空探索:抗辐射剂量>1MEV/cm²

NASA的JPL火星探测器搭载异步处理器,在深空辐射环境下MTBF达到15年。

技术演进趋势分析

-

混合架构的兴起 (1)时间片轮转机制:将系统划分为同步/异步时隙 (2)动态切换策略:基于负载类型自动选择架构 (3)案例:Apple M2 Ultra采用4核同步+8核异步混合架构,性能提升23%,功耗降低18%

-

先进封装的融合创新 (1)晶圆级封装(WLP):实现同步/异步模块的物理隔离 (2)3D IC堆叠:通过硅通孔(TSV)连接不同架构模块 (3)技术突破:台积电SoIC技术使异构模块集成度提升40%

-

量子计算的启示 (1)量子门操作时序:采用异步量子门序列 (2)经典-量子接口:通过异步握手实现状态传输 (3)实验数据:Google Sycamore处理器异步接口降低量子纠错功耗达62%

结论与展望 同步主机与异步主机的本质差异在于时序控制范式的根本性区别,这种差异在物理形态上呈现为电路拓扑和接口设计的系统性差异,现代封装工艺和功能复用技术正在模糊两者的外观界限,未来技术发展将呈现三大趋势:异构混合架构的普遍化、事件驱动设计的低功耗化、先进封装下的形态融合化。

对于工程师而言,选择架构时应建立多维评估体系:

- 实时性需求(同步优势:确定性延迟;异步优势:动态响应)

- 功耗约束(同步功耗模型:P_sync = C_vdd² f_clock;异步模型:P_async = C_vdd² f_event * λ)

- 可靠性要求(同步容错:ECC/重试机制;异步容错:动态重握手)

- 生态成熟度(同步:EDA工具链完善;异步:IP核支持度<60%)

建议在以下场景优先考虑异步主机:

- 事件驱动型应用(传感器数据流处理)

- 极端低功耗需求(医疗植入设备)

- 高度动态的时序要求(自动驾驶决策系统)

而在以下场景推荐同步主机:

- 高吞吐计算密集型任务(HPC/AI训练)

- 严格实时性约束场景(航空航天控制系统)

- 生态成熟度要求高的领域(企业级服务器)

技术选型应超越外观辨识的表层,深入理解两种架构的底层逻辑,建立基于系统级优化的决策模型,随着Chiplet技术和光互连的发展,未来主机形态将更加模块化,但架构选择的根本原则仍将回归到"正确性、性能、成本"的三维平衡。

本文链接:https://www.zhitaoyun.cn/2328152.html

发表评论